DOI:10.13875/j.issn.1674-0637.2019-02-0142-09

# 基于 FPGA 的 TDC 系统偏差修正方法的研究<sup>\*</sup>

刘正阳<sup>1,2</sup>, 刘音华<sup>1,2,3</sup>, 李孝辉<sup>1,2,3,4</sup>

(1. 中国科学院 国家授时中心, 西安 710600;

2. 中国科学院大学, 北京 100049;

3. 中国科学院 时间基准频率重点实验室, 西安 710600;

4. 中国科学院大学 天文与空间科学学院, 北京 101048)

**摘要:**随着 TDC(time-to-digital converter)技术的广泛应用,对其精度的要求也越来越高。系统偏差作为 TDC 测量中不可避免的误差,通常由硬件结构、电路走线、测量过程等过程引入,其是否可以被有效修正直接影响着测量精度。为此,分析了基于 FPGA(field-programmable gate array)的时间间隔测量的工作原理及系统组成,并搭建了硬件测试平台,进行了一系列时间间隔测量实验及系统偏差分析,结合 FPGA 测量原理,绘出了系统偏差修正方案并评估了时间间隔测量精度的影响。实验表明,建立有效的一次模型对测量结果进行拟合并对测量结果进行修正,可以将系统偏差控制在 100 ps 以下,提高 TDC 测量准确度。

**关键词:**现场可编程门阵列;时间数字转换技术;系统偏差;准确度

## TDC system deviation correction method research based on FPGA

LIU Zheng-yang<sup>1,2</sup>, LIU Yin-hua<sup>1,2,3</sup>, LI Xiao-hui<sup>1,2,3,4</sup>

(1. National Time Service Center, Chinese Academy of Sciences, Xi'an 710600, China;

2. University of Chinese Academy of Sciences, Beijing 100049, China;

3. Key Laboratory of Time and Frequency Primary Standards, Chinese Academy of Sciences, Xi'an 710600, China;

4. School of Astronomy and Space Science, University of Chinese Academy of Sciences, Beijing 101048, China)

**Abstract:** With the extensive application of time-to-digital converter (TDC) technology, the requirements for the accuracy of TDC are also increasing. The system deviation, as an inevitable deviation in TDC measurement, is mostly introduced by the hardware structure, circuit line, measurement process, etc. Whether it can be effectively modified directly affects the measurement accuracy. Therefore, in this paper, we analyze the working principle and system composition of time interval measurement based on field-programmable gate array(FPGA). Meanwhile, a hardware test platform is built to conduct a series of time-interval measurement experiments and system deviation analysis, and combined with FPGA measurement principle to draw up the system deviation correction program and evaluate the impact of the time-interval measurement. Experiments show that if an effective model can be established to fit the measurement results and correct the measurement results, it can hold the system deviation below 100ps. As a result, the accuracy of TDC is significantly improved.

\* 收稿日期:2018-11-18;接受日期:2019-01-09

基金项目:中国科学院“西部之光”人才培养计划西部青年学者 A 类资助项目(XAB2016A05)

作者简介:刘正阳,女,硕士,主要从事时间间隔测量研究。

**Key words:** field-programmable gate array (FPGA); time-to-digital converter (TDC); system deviation; accuracy

## 0 引言

TDC(time-to-digital converter)是将时间间隔模拟量转换为数字量的一种时间数字转换器<sup>[1]</sup>。随着科技的高速发展,时间数字转换器已广泛应用于高能物理实验、通信、卫星导航等诸多领域,且根据不同的应用场合,对其测量精度也提出了越来越高的要求。

为了提升时间数字转换分辨率,当前的主流方法大致分为两种,一种是将待测时间“放大”,在现有的分辨率下进行测量,比如时间延展法;另一种是寻找尽可能小的时间分度来测量时间间隔,比如时间内插法。

利用延迟链技术的时间内插方法,因其可以实现较高的时间精度,近些年来得到迅速的发展和应用<sup>[2]</sup>。插值法将大步长计数和精密测量结合起来,既能获得较大的动态范围,也能达到较高的时间精度。对于插值法,延时单元的一致性、精确度决定了 TDC 的时间分辨能力。

目前高分辨率的 TDC 主要在 ASIC 芯片上实现的,但 ASIC 芯片价格昂贵,开发周期长。而基于 FPGA(field-programmable gate array)芯片实现的 TDC 成本低,开发周期短,设计灵活,近年来受到广泛关注<sup>[3]</sup>。

但是,基于 FPGA 芯片实现的 TDC 存在着较大的系统偏差,以基于 FPGA 加法进位链的时间间隔测量系统为例,FPGA 的工艺、仪器偏差、外部硬件电路的走线等都影响着测量结果。而这些偏差对于高精度时间间隔计数器而言,将会产生明显的影响。

因此为了提高时间间隔测量系统的性能,对时间间隔测量系统的系统偏差进行校准是十分重要的,本文以 Altera 公司的 Cyclone IV EP4CGX150DF31C7 为实验芯片,通过实验分析得出了系统偏差修正的合理方案,并计算出不同参考时钟下的系统偏差拟合模型,进一步提高测量的准确度。

## 1 时间间隔测量原理

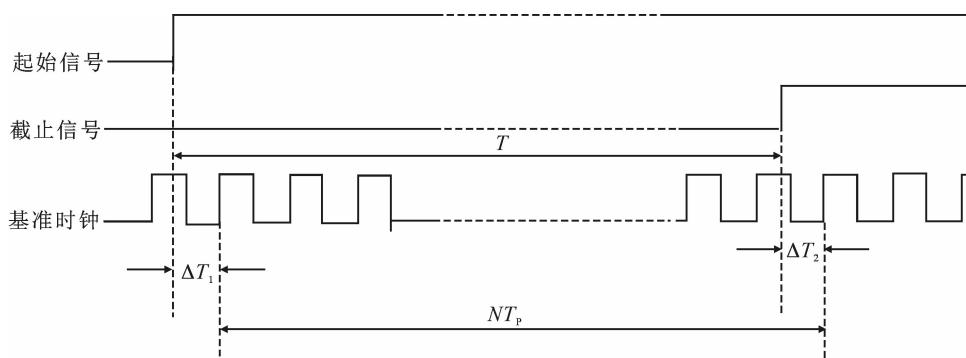

本文所研究的计数器采用的时间间隔测量基本思路如图 1 所示,为兼顾量程和测量分辨率,将测量分为粗测量和细测量两部分。

首先,粗测量测量起始信号和截止信号的时间间隔,由起始信号开门,以截止信号关门,在此时间段内,时基脉冲进入计数器,若时基脉冲周期为  $T_p$ ,计数器指示值为  $N$ ,则待测时间间隔粗测量结果为  $NT_p$ <sup>[4]</sup>。

待测时间间隔的细测量包括两个部分,一是测量开始信号上升沿相对于下一个基准时钟上升沿之间的时间间隔  $\Delta T_1$ ,另一个是测量截止信号上升沿相对于下一个基准时钟上升沿之间的时间间隔  $\Delta T_2$ ,本文所设计基于 FPGA 内部加法进位延迟链资源实现时间的精密内插,从而实现  $\Delta T_1$  和  $\Delta T_2$  的细测量<sup>[5]</sup>。

图 1 时间间隔测量基本思路

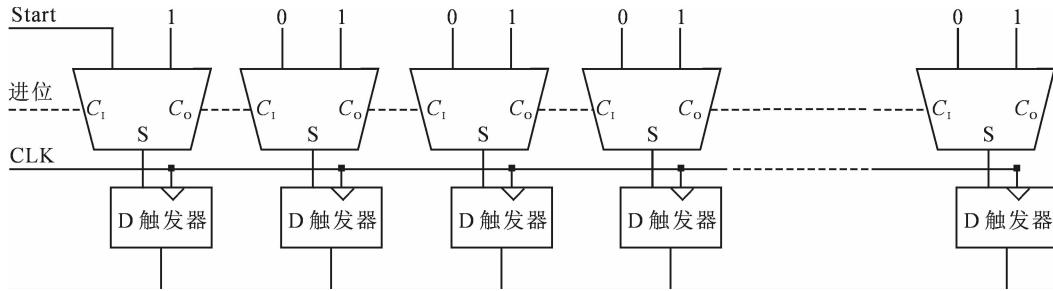

细测量的基本延迟单元由加法进位延迟链构成,通过对延迟单元的个数进行计数再乘以平均延迟即可获得测量结果。以测量起始信号上升沿相对于下一个基准时钟上升沿之间的时间间隔 $\Delta T_1$ 为例,如图 2 所示,在 FPGA 内设计一个串行多位加法器将专用进位链级联,第一级加法器的两个输入端分别接 Start 信号和一个高电平信号,其他加法器的两个输入端一个接高电平,一个接低电平,当 Start 信号上升沿到来,进位信号就能在所构建的进位链中传播,通过一组 D 触发器捕捉时钟 CLK 上升沿到来时刻进位信号所在的位置。如果进位链上每个延时单元的延时已知,就可以求得 Start 上升沿和下一个的 CLK 上升沿之间的时间间隔。本文所构建的加法进位链级数为 96 级,各进位单元时延不完全相等,每级时延在 30~68 ps 之间,平均延时为 42 ps,因此可以实现 100 ps 以下的测量分辨率。

图 2 细测量的基本原理

在计算各级进位链时延的过程中,CLK 信号到每个 D 触发器时延的影响主要集中在第一级进位链,这是因为 CLK 信号到每个 D 触发器的时延相同,当信号传播到第  $N$  级( $N > 1$ )进位链时,可以通过与信号传播到第  $N-1$  级进位链的时延进行计算,得到抵消了 CLK 信号到 D 触发器时延的第  $N$  级进位链的时延,而第一级中 CLK 信号到 D 触发器时延则计入到第一级进位链时延中。由于测量截止信号与时钟上升沿之间  $\Delta T_2$  的时间间隔原理与起始信号相同<sup>[6]</sup>,因此在计算时间间隔测量结果  $T = NT_p + \Delta T_1 - \Delta T_2$  时,这部分时延也在计算  $\Delta T_1 - \Delta T_2$  的过程中抵扣,因此 CLK 信号到每个 D 触发器的时延对测量结果不会产生影响。

## 2 基于 FPGA 的 TDC 的设计与测试平台搭建

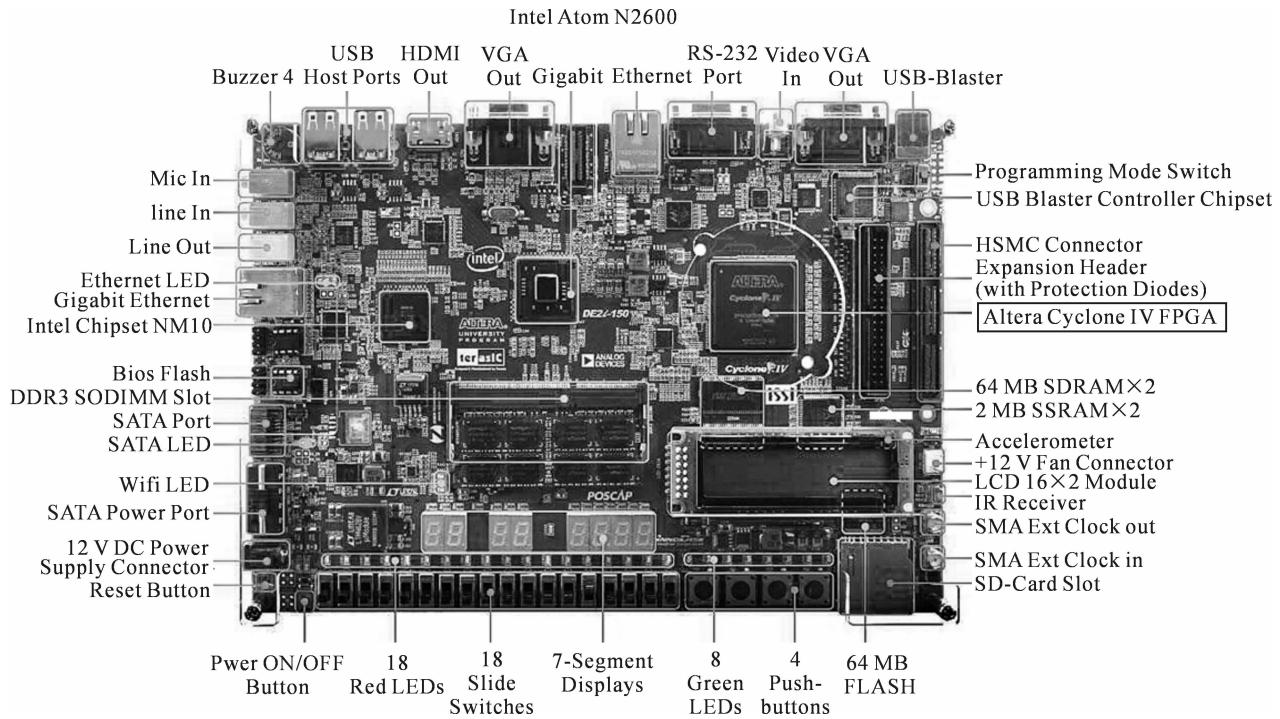

本文中提出的 FPGA 设计在友晶公司的 DE2i-150 开发板上实现,系统程序采用 Verilog HDL 语言。如图 3 为开发板正面图示,所使用的 Altera 公司的 Cyclone IV EP4CGX150DF31C7 为图中右侧所圈注示意的。开发板上配有 SMA 连接件,可支持外部参考时钟的输入。

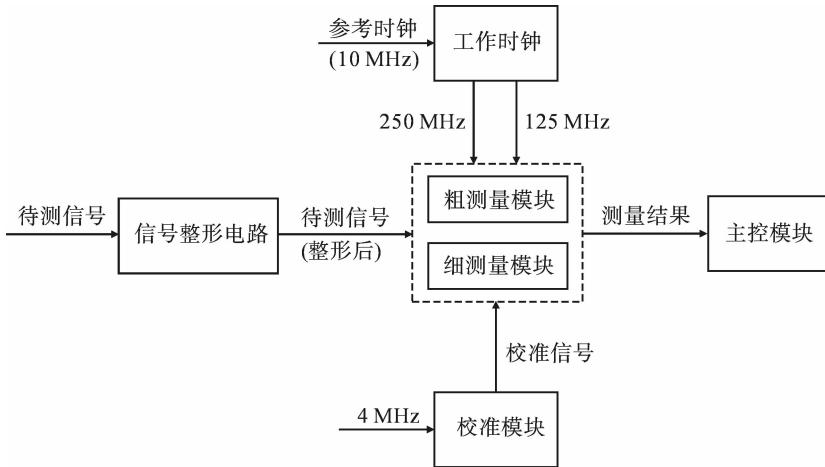

基于 FPGA 的时间间隔测量系统的设计构架如图 4 所示。工作时钟由外部输入或板载晶振产生的 10 MHz 参考时钟进行倍频产生,输入到 FPGA 开发板的数模转换电路,选用高稳定度的原子钟可以有效地保证参考时钟信号的频率稳定性。具体实现时采用锁相环对输入的 10 MHz 参考时钟进行倍频,输出稳定的 125 MHz 系统工作主时钟。同时,锁相环模块还需产生 250 MHz 的粗计数时钟。锁相环所产生的本片 FPGA 工作所需的基础<sup>[7]</sup>。

在开始测量前,信号整形电路实现对待测的开始和截止信号进行整形、滤波和模数转换,转换成稳定的数字信号后送给 FPGA 的测量起始信号与截止信号引脚,组成两路测试通道进行时间间隔测量。

根据上节时间间隔测量原理,本文所设计的时间间隔测量系统的测量功能采用粗测量和细测量相结合的思路。粗测量的工作时钟频率为 250 MHz,周期为 4 ns,位宽为 28 bit,可以满足 1 s 的量程指标要求,此时误差在正负 1 个时钟周期。分辨率主要由细测量模块的加法进位延迟单元的时延所决定,因此采用基于 FPGA 进位链的细测量模块来对 1 个时钟周期内的时间间隔进行测量,把测量误差控制在 1 个时钟周期以内。

图3 开发板正面示意图

图4 基于FPGA的时间间隔测量系统设计架构框图

校准模块采用4 MHz晶振作为校准信号的产生源,校准晶振的输出频率为4 MHz,为加法进位延迟链提供校准信号,产生相对于FPGA内部工作时钟的随机脉冲信号,采用码密度测试方法对加法进位延迟链进行校准,减少细测量模块的测量误差。

时间间隔测量系统在工作时,通过主控模块实现与FPGA的通信<sup>[8]</sup>。根据不同情况下的功能所需,CPU采用两种接口方式实现与FPGA的数据通信,一种为寄存器寻址方式,使FPGA和CPU均可以访问、读写,存储内容包括FPGA时间间隔测量结果,CPU向FPGA发送的各项指令数据等等。CPU和FPGA另一种接口方式为信号管脚直连方式,包括各种中断信号和FPGA的全局复位信号。FPGA片内的各个模块的测试,主要由Quartus II的逻辑分析仪SignalTap来实现数据采集和分析,使用QuartusII软件可以在任何时间重新配置FPGA。

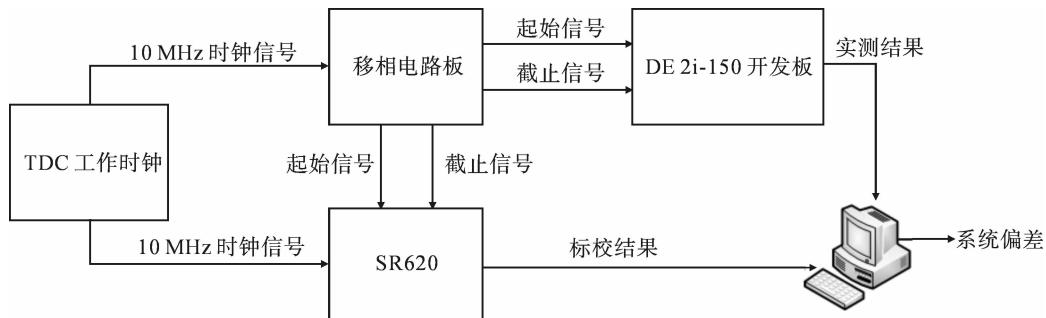

为了进一步减少基于FPGA加法进位链的时间间隔测量系统的测量误差,提高测量精度,故在得到测量结果后仍需对其进行偏差校正,为得出有效的系统偏差校准方案,搭建了如图5所示的测试平台。

图 5 时间间隔测量系统测试平台连接示意图

移相电路板用于产生待测时间间隔,其工作芯片为 EPM240T100C5N,上电后通过运行在通用计算机上的程序来控制产生不同的待测时间间隔。其最小步进为 100 ns,产生时间间隔范围为 100~999,999,900 ns。

测试开始时需首先对待测时间间隔进行标校,标校所使用的仪器为美国斯坦福公司的 SR620 时间间隔计数器,SR620 在时间间隔测量方式下单次时间分辨率为 25 ps,最小有效数据为 4 ps。因其是当前国际主流时间间隔测量仪器,测量精确度高于所设计计数器,故将其测量输出的结果作为待测时间间隔的测量参考真值。

标校开始时,首先使用移相电路板产生已知时间间隔,将待测通道的开始与截止信号分别接入 SR620 进行测量,均取 1 min 的观测平均值作为该时间间隔的参考值。

将待测信号接入 FPGA 板,为了消除毛刺防止误检,输入信号首先需经过信号整形模块进行预处理,然后将整形后的起始信号与截止信号输入到粗测量模块和细测量模块,对计数器的各通道进行测量,每个时间间隔采样时间为 1 min。测量结果按照规定的格式经串口程序输出到通用计算机<sup>[9]</sup>。

通用计算机作为 FPGA 开发板和数据采集软件等的运行平台,每当 FPGA 加电时就可以实现与 FPGA 的通信。运行在计算机上的程序对数据进行解算处理,按照测量原理得到实际测量结果,与参考值进行比对,分析系统偏差<sup>[10]</sup>。

### 3 系统偏差的来源与修正方法

对于基于 FPGA 加法进位链的时间间隔测量系统来说,仪器偏差一个主要来源是延迟链的延迟单元,因 FPGA 中的进位链或其他逻辑资源形成的延迟单元都不是十分稳定,另外型号不同、速度等级不同也会影响延迟,除此之外,由于生产制造工艺的影响,即使是同一型号的器件的延迟也一定存在着差异。

除了 FPGA 芯片,外部电路的走线、测量过程的准确性同样影响着测量结果。例如开始信号、截止信号在外部硬件电路中的走线延迟不可能完全相等,测量和校准过程等存在不确定性,这些都会在最后的测量结果中引入系统偏差。

硬件线路的走线延迟与进位链引入的偏差属于稳定的系统差,可以通过测量已知时间间隔来修正。实验发现 TDC 工作时钟漂移引入的偏差并不是一个常量,随着待测时间间隔的变化而变化,这种现象在高精度的 TDC 工作时钟下并不明显,例如氢钟、铯钟,但是对于铷钟或是晶振作为工作时钟时,随着测量时间间隔增加将表现得非常明显。

为了得到有效的偏差修正方案,在测量范围 0~1 s 内对一系列时间间隔进行测试,对系统偏差进行分析。

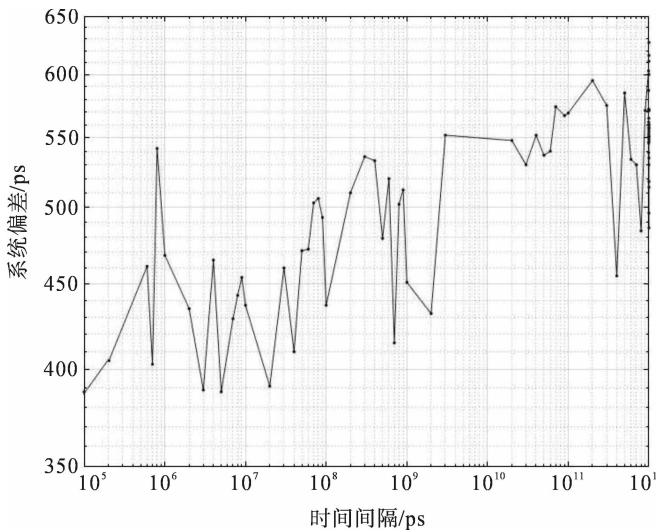

图 6 为铯钟作为 TDC 工作时钟时的不同待测时间间隔的系统偏差图,图中所示为取双对数坐标后的结果,纵坐标为系统偏差,横坐标为待测时间间隔。此时偏差主要分布在 350~650 ps 之间左右,偏差平均值为 514 ps,由图可看出二者之间存在着线性关系。

图6 锆钟作为TDC工作时钟时的系统偏差

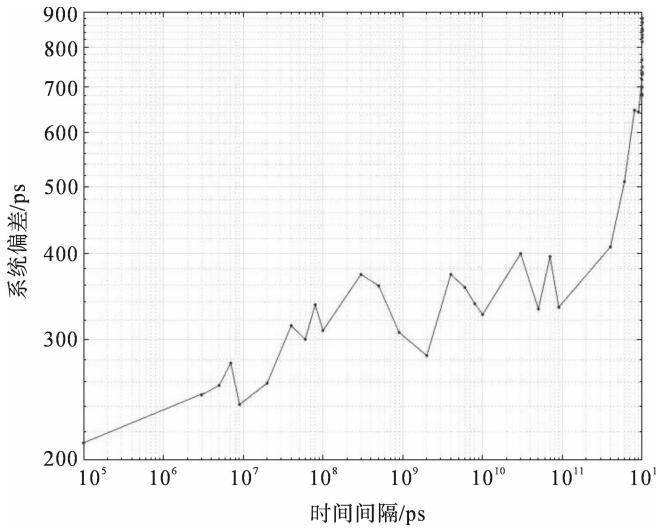

图7为铷钟作为TDC工作时钟时的不同待测时间间隔的系统偏差双对数坐标图,此时系统偏差分布在200~900 ps之间,系统偏差平均值为555 ps。可以看出相比于铯钟,随着待测时间间隔的增加,铷钟系统偏差的增大趋势更为明显。

图7 铷钟作为TDC工作时钟时的系统偏差

由此可知,TDC工作时钟的准确度对TDC测量偏差有直接贡献,为降低不同准确度的工作时钟对TDC系统偏差的影响,提出一种线性拟合校准系统偏差的方法。在一次线性拟合中,对于硬件电路延迟等引起的系统偏差将在常数项中得以校正,TDC工作时钟的影响主要由一次项系数进行校正。

#### 4 系统偏差校正方案验证

为验证校正方案的有效性进行了以下3组实验:首先以铯钟作为工作时钟在量程范围内选取不同时间间隔进行测试并得出一次拟合模型,其次以铷钟作为工作时钟在量程范围内选取不同时间间隔进行测试并得出一次拟合模型,最后选取任意时间间隔对不同工作时钟下的一次拟合模型进行验证。

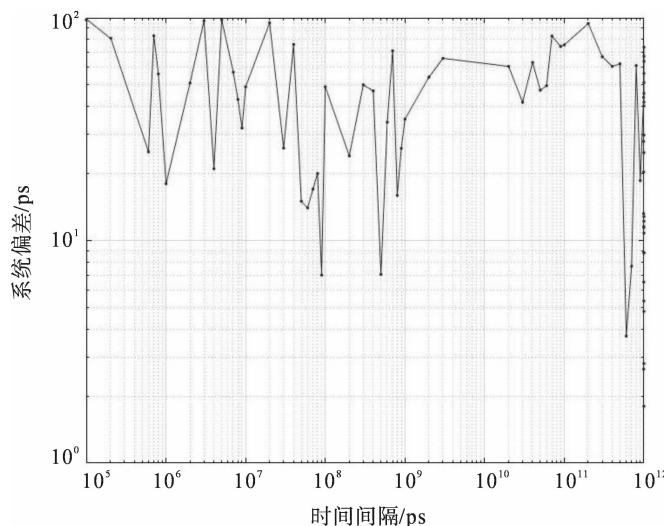

根据所测得的样本数据通过最小二乘的方法建立一次模型,对于铯钟来说拟合的直线方程为 $y = 7.38 \times 10^{-11}x + 486$ ,其斜率为 $7.38 \times 10^{-11}$ 。根据方程求出拟合后的系统偏差修正量,得到修正后的系统偏差,表1为以铯钟作为TDC工作时钟时的0~1 s测量范围内不同待测时间间隔的系统偏差与修正后结果的对比,通过一次线性拟合,将系统偏差降至100 ps以下。整个区间所有测试值的系统偏差拟合修正后的

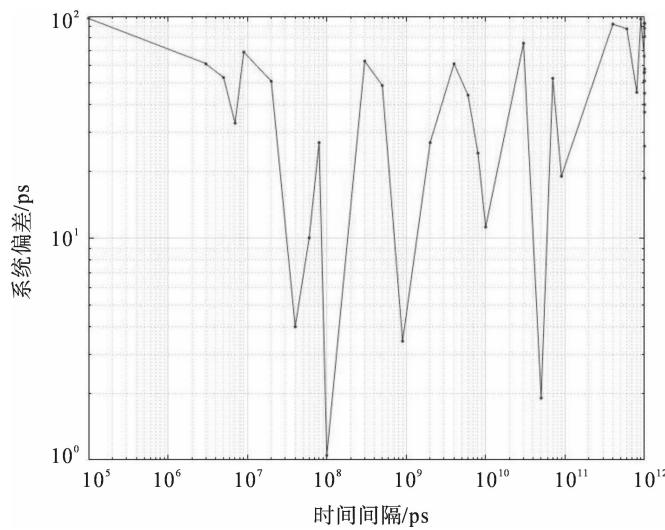

结果如图 8 所示,此时整个测量范围所有测试值的系统偏差平均值为 39 ps。本文中所有系统偏差均指实际测量值减去标校真值的结果,在对数坐标系中作图时负值使用绝对值表示。

表 1 以铯钟作为 TDC 工作时钟时拟合修正情况 ps

| 序号 | 时间间隔实测值         | 系统偏差 | 拟合后系统偏差 |

|----|-----------------|------|---------|

| 1  | 803 224         | 542  | 56      |

| 2  | 7 002 864       | 429  | -57     |

| 3  | 50 002 956      | 471  | -15     |

| 4  | 400 003 241     | 533  | 47      |

| 5  | 40 000 003 496  | 552  | 63      |

| 6  | 300 000 003 299 | 575  | 66      |

| 7  | 997 000 003 371 | 571  | 11      |

| 8  | 999 996 003 482 | 551  | -9      |

| 9  | 999 999 403 220 | 616  | 56      |

| 10 | 999 999 903 489 | 486  | -74     |

图 8 整个区间内铯钟作为 TDC 工作时钟时的系统偏差

对于铷钟来说拟合的直线方程为  $y=4.78 \times 10^{-10}x+310$ ,其斜率为  $4.78 \times 10^{-10}$ 。表 2 为以铷钟作为 TDC 工作时钟时的 0~1 s 测量范围内不同待测时间间隔的系统偏差与修正结果的对比,可以看出,通过一次线性拟合其结果同样得到显著改善,此时系统偏差平均值为 49 ps。整个区间所有测试值的系统偏差拟合后的结果如图 9 所示。

表 2 以铷钟作为 TDC 工作时钟时拟合修正情况 ps

| 序号 | 时间间隔实测值         | 系统偏差 | 拟合后系统偏差 |

|----|-----------------|------|---------|

| 1  | 40 003 715      | 314  | 4       |

| 2  | 500 003 488     | 359  | 49      |

| 3  | 6 000 003 405   | 357  | 44      |

| 4  | 30 000 003 333  | 400  | 76      |

| 5  | 70 000 003 279  | 396  | 53      |

| 6  | 800 000 004 154 | 647  | -45     |

| 7  | 992 000 003 770 | 733  | -51     |

| 8  | 996 000 003 885 | 735  | -51     |

| 9  | 999 993 003 629 | 833  | 45      |

| 10 | 999 999 704 076 | 850  | 62      |

图 9 整个区间内铷钟作为 TDC 工作时钟时的系统偏差

除此之外,另取测量区间内由小到大任意 10 组时间间隔进行验证,结果分别如表 3 及表 4 所示。

表 3 以铯钟作为 TDC 工作时钟时任意间隔修正后结果 ps

| 序号 | 时间间隔测量值         | SR620 真值        | 系统偏差 |

|----|-----------------|-----------------|------|

| 1  | 1 102 691       | 1 102 654       | 37   |

| 2  | 7 202 436       | 7 202 374       | 62   |

| 3  | 40 103 323      | 40 103 268      | 55   |

| 4  | 200 303 090     | 200 303 102     | -12  |

| 5  | 5 000 402 786   | 5 000 402 726   | 60   |

| 6  | 60 000 602 433  | 60 000 602 366  | 67   |

| 7  | 400 000 403 228 | 400 000 403 251 | -23  |

| 8  | 980 000 002 216 | 980 000 002 139 | 77   |

| 9  | 999 800 102 238 | 999 800 102 213 | 25   |

| 10 | 999 899 002 652 | 999 899 002 612 | 40   |

表 4 以铷钟作为 TDC 工作时钟时任意间隔修正后结果 ps

| 序号 | 时间间隔测量值         | SR620 真值        | 系统偏差 |

|----|-----------------|-----------------|------|

| 1  | 1 102 236       | 1 102 210       | 26   |

| 2  | 7 203 244       | 7 203 192       | 52   |

| 3  | 40 103 432      | 40 103 385      | 47   |

| 4  | 200 303 212     | 200 303 153     | 59   |

| 5  | 5 000 402 531   | 5 000 402 467   | 64   |

| 6  | 60 000 603 266  | 60 000 603 319  | -53  |

| 7  | 400 000 403 130 | 400 000 403 175 | -45  |

| 8  | 980 000 002 249 | 980 000 002 316 | -67  |

| 9  | 999 800 103 655 | 999 800 103 606 | 49   |

| 10 | 999 899 002 587 | 999 899 002 542 | 45   |

综上所述,本文所建立的一次模型可以有效的将偏差修正到 100 ps 以下。

## 5 结论

本文通过探究基于 FPGA 的 TDC 系统偏差的修正方法,对基于 Cyclone IV EP4CGX150DF31C7 的时间间隔测量系统在使用铯钟及铷钟为工作时钟时的不同测量结果进行了分析,根据系统在整个测量范围内的偏差呈线性化趋势,设计了一次拟合校正方法,通过不同实验对校正值进行了测量,利用校正后的计数器进行了测试实验,验证了系统偏差修正方案的正确性,使系统偏差控制在 100 ps 以下,在实际应用中,可将一次线性拟合模型参数写入 CPU 以实现系统偏差校正,提高时间间隔测量的准确度,更好地发挥芯片的性能。

## 参考文献:

- [1] 蒋旻. 基于时域量化的逐次逼近型 ADC 研究与设计[D]. 成都: 电子科技大学, 2015.

- [2] 黄海舰. 基于 FPGA 时间内插技术的 TDC 设计[D]. 武汉: 华中师范大学, 2013.

- [3] 张敏. 皮秒分辨率的 FPGA-TDC 技术研究[D]. 西安: 西安电子科技大学, 2013.

- [4] 李亚胜. 一种高精度时间间隔测量板卡设计[J]. 西安航空学院学报, 2015, 33(5): 65-68.

- [5] 宋健. 基于 FPGA 的精密时间—数字转换电路研究[D]. 合肥: 中国科学技术大学, 2006.

- [6] 张朗. 基于 FPGA 的高精度测时仪研制[D]. 南京: 南京理工大学, 2012.

- [7] 王忠涛, 杨明武. 可实现快速锁定的 FPGA 片内延时锁相环设计[J]. 电子科技, 2010, 23(4): 45-49.

- [8] 王晓飞, 张伏江, 梁福平. 基于多 CPU 和 PCI 的高速海量温湿度测量系统设计[J]. 仪表技术与传感器, 2013(11): 56-58, 61.

- [9] 陆维佳, 潘玉. FPGA 设计中毛刺问题的研究[J]. 现代电子技术, 2005(9): 36-38, 41.

- [10] 张志杰, 汪翔. 如何解决 FPGA 电路设计中的毛刺问题[J]. 世界电子元器件, 2004(11): 68-69, 72.